# PHY335 Spring 2022 Lecture 7

Jan C. Bernauer

SH P

April 2022

- Analog signals degenerate through noise.

- Replace continuous analog signal levels with only two, discrete levels (/windows/ranges)

- Analog signals degenerate through noise.

- Replace continuous analog signal levels with only two, discrete levels (/windows/ranges)

- These are called logic states

- HIGH vs. LOW (voltage level)

- TRUE vs. FALSE (Boolean logic)

- Analog signals degenerate through noise.

- Replace continuous analog signal levels with only two, discrete levels (/windows/ranges)

- These are called logic states

- HIGH vs. LOW (voltage level)

- TRUE vs. FALSE (Boolean logic)

- A system where HIGH represents TRUE is called active-high, a system where LOW represents TRUE is called active-low

#### Voltage ranges for HIGH and LOW

- Separate for input and output: Allows a bigger range for input than guarantees for the output.

- This gives noise immunity

- Classic: TTL (Transistor-Transistor-logic):

- Input: <+0.8V is low, >+2.0V is high (meaning that a TTL compatible device is allowed to transition from low to high anywhere between 0.8 and 2V

- Output worst case: low +0.4V, high +2.4V

- So only 0.4V worst-case voltage margin

- CMOS has better voltage-noise immunity (for same V<sub>DD</sub>) and wider V<sub>DD</sub> range. Ranges for 5V:

- Input: 0-1.5V low, 3.5 to 5 high

- Output: 0-0.05V low, 4.95 to 5 V high.

- Originally 74YYXX, where XX represents the code number for different functions.

- Series: YY

- Nothing: original TTL, 10ns propagation delay, 25 MHz operation, 5V

- L(S): Low power TTL: 33ns , 3MHz, 1/10 of power

- H: high speed TTL, 6ns, 43MHz, 2.2x power

- F: Fast TTL, 3.5ns, 100MHz, but 1/2x power!

- HC(T): High speed CMOS, 9 ns, 50MHz, 1/20 of power. T has TTL compatible voltage levels

- AC(T): Advanced CMOS, 3 ns, 125MHz, 1/20 of power, typically 3.3V or 5V

There are also other logic series like the 4000 CMOS series

- ECL (Emitter-coupled-logic): ECL (negative power supply), PECL (positive supply) Less noise immunity, a lot of power required, but very very fast

- NIM logic (Nuclear Instrumentation Module): active-low!

- Many many CMOS variants with higher speed, lower power, lower V<sub>CC</sub> etc.

Combinatorical logic is logic which only acts on the current state of signals. There is no history/memory.

(The delay between change of input and change of output is called the propagation delay)

We can build any function out of some standard building blocks!

Represent the function in a table. Short hand: we can represent the logic state TRUE/FALSE with a binary digit, 1=TRUE, 0=FALSE

| А | В | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

• Y = A + B

•  $Y = A \cdot B = AB$

#### Inverter gate "NOT"

A Y 0 1 1 0

•  $Y = \overline{A} = /A = *A =$  $A' = -A = \sim A = !A$

### XOR gate (exclusive or)

| А | В | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

- $Y = A \otimes B = A^{A}B$

- This is often used in cryptography:

$A \otimes B \otimes B = A$

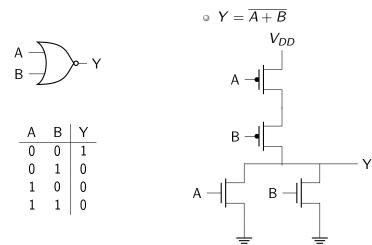

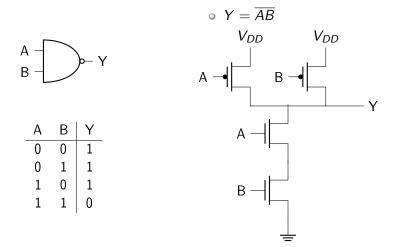

De Morgan's theorem:

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

$$\overline{A+B} = \overline{A} \cdot \overline{B}$$

De Morgan's theorem:

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

$$\overline{A+B} = \overline{A} \cdot \overline{B}$$

This means that having inverters and one of OR / AND is enough to produce all logic functions!

De Morgan's theorem:

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

$$\overline{A+B} = \overline{A} \cdot \overline{B}$$

This means that having inverters and one of OR / AND is enough to produce all logic functions!

Since a NAND or NOR with both inputs tied together is an inverter, one can build all logic functions just with NAND or NOR gates!

- ABC = (AB)C = A(BC)

- AB = BA

- AA = A

- $\circ A1 = A$

- A0 = 0

- A(B+C) = AB + AC

- A + AB = A

- A+BC = (A+B)(A+C)

- A + B + C =(A+B)+C = A+(B+C)

- A + B = B + A

A + A = A

A + 1 = 1

- A + 0 = A

- $\overline{1} = 0$

- 0̄ = 1

- $A + \overline{A} = 1$

- $A\bar{A} = 0$

- $\bar{\bar{A}} = A$

• For each line where the output is 1, write an AND of all input variables, negate them if the truth table is 0 for them.

- For each line where the output is 1, write an AND of all input variables, negate them if the truth table is 0 for them.

- OR all terms.

- For each line where the output is 1, write an AND of all input variables, negate them if the truth table is 0 for them.

- OR all terms.

- Simplify, with an eye on what gates you have, and what signals you already have in your circuit

| А | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

$$Y = (ar{A}ar{B}C) + (ar{A}Bar{C}) + (ar{A}BC) + (ABC)$$

$$egin{aligned} Y &= (ar{A}ar{B}C) + (ar{A}Bar{C}) + (ar{A}BC) + (ABC) \ Y &= ar{A}(ar{B}C + Bar{C} + BC) + ABC \end{aligned}$$

$$Y = (\overline{ABC}) + (\overline{ABC}) + (\overline{ABC}) + (ABC)$$

$$Y = \overline{A}(\overline{BC} + B\overline{C} + BC) + ABC$$

$$Y = \overline{A}(\overline{BC} + B) + ABC$$

| А | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

$$Y = (\overline{ABC}) + (\overline{ABC}) + (\overline{ABC}) + (ABC)$$

$$Y = \overline{A}(\overline{BC} + B\overline{C} + BC) + ABC$$

$$Y = \overline{A}(\overline{BC} + B) + ABC$$

$$Y = \overline{A}(B + C) + ABC$$

## **Binary Numbers**

• Represent integers in base 2:  $6_{10} = 110_2 = b110 = 1 \times 2^2 + 1 \times 2^1 + 0 \times 2^0$

## **Binary Numbers**

- Represent integers in base 2:  $6_{10} = 110_2 = b110 = 1 \times 2^2 + 1 \times 2^1 + 0 \times 2^0$

- Each binary digit can be a signal

- An array of signal can represent an integer in a certain range

## Binary Numbers

- Represent integers in base 2:  $6_{10} = 110_2 = b110 = 1 \times 2^2 + 1 \times 2^1 + 0 \times 2^0$

- Each binary digit can be a signal

- An array of signal can represent an integer in a certain range

- Common names:

- 1 bit: 1 signal

- Nibble: 4 bit

- Byte: 8 bit

- Word (architecture dependent, but often): 16 bit

- DWORD (double word) 32 bit

- Most significant bit (MSB): Highest valued bit

- Least significant bit (LSB): bit with value 1

- Often use hexadecimal: 1 hexadecimal digit (0-9,A-F) maps directly to a nibble. 0xFF=255=0b1111 1111

- 0xA=? =10=0b1010

- 0b1110=?

- 0xA=? =10=0b1010

- 0b1110=?=14

- 0xA=? =10=0b1010

- 0b1110=?=14=0×E

- 0b1111 1111 1111 1111= 0xffff=2<sup>16</sup>-1=65535

- Sign-magnitude: one bit for sign, remaining bits for magnitude

- Offset binary: 0b1000=0, 0b1001=1, 0b0111=-1

- 2's complement: 0b0111=7, 0b0000=0, 0b1111=-1,0b1000=-8

Often 2's complement is used often because it simplifies arithmetic and has no doubled zero.

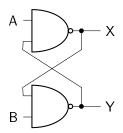

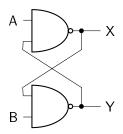

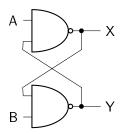

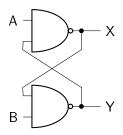

#### Sequential logic & one bit memory: flip-flops

The Reset-Set Flip-Flop: RS-FF

### Sequential logic & one bit memory: flip-flops

The Reset-Set Flip-Flop: RS-FF

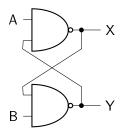

•

$$X = \overline{AY} = \overline{A} + \overline{Y}$$

,

$Y = \overline{BX} = \overline{B} + \overline{X}$

The Reset-Set Flip-Flop: RS-FF

- $X = \overline{AY} = \overline{A} + \overline{Y},$  $Y = \overline{BX} = \overline{B} + \overline{X}$

- Assume we put A low:

- X must be high, Y depends on what B is.

The Reset-Set Flip-Flop: RS-FF

- $X = \overline{AY} = \overline{A} + \overline{Y},$  $Y = \overline{BX} = \overline{B} + \overline{X}$

- Assume we put A low:

- X must be high, Y depends on what B is.

- Assume we put B low:

- Y must be high, X depends on what A is.

### Sequential logic & one bit memory: flip-flops

The Reset-Set Flip-Flop: RS-FF

$$X = \overline{AY} = \overline{A} + \overline{Y}$$

$$Y = \overline{BX} = \overline{B} + \overline{X}$$

• Assume we put A and B HIGH. Two possibilities:

- X is high. This means Y has to be LOW, which is fine, because both B and X are high

- X is low. This means that Y has to be HIGH.

- X and Y can not both be LOW (or HIGH) at the same time!

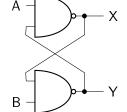

# Sequential logic & one bit memory: flip-flops

The Reset-Set Flip-Flop: RS-FF

Assume we put A and B HIGH. Two possibilities:

- X is high. This means Y has to be LOW, which is fine, because both B and X are high

- X is low. This means that Y has to be HIGH.

- X and Y can not both be LOW (or HIGH) at the same time!

- So the circuit is bi-stable. It depends on the history whether X is HIGH or LOW

- Normal state: S

<sup>-</sup> and R

<sup>-</sup> is high. Q and Q

stay constant.

- Setting  $ar{S}$  low sets the FF, so Q goes high

- Setting  $\overline{R}$  low reset the FF, so Q goes low

- Setting  $ar{S}$  and  $ar{R}$  low at the same time is a forbidden state (Because then  $Q=ar{Q})$

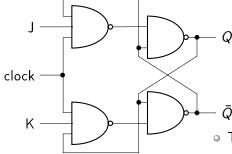

# Clocked flip flops: JK

- If clock is low, nothing happens

- if clock is high,

- J and K are low: nothing happens

- J high: If Q is low, S goes low, Q goes high, S goes high, then nothing happens

- K high: If Q is high, Q goes low, then nothing happens

- J and K are high: Q

- toggles/oscillate

- Two fixes:

- Short clock high periods (e.g. with a capacitor)

- Master-slave config (two JK in series, with inverted clock)

- Take a MS JK flip flop. Rename J to D, and connect K to an inverted D

- D is the data line. On every clock edge, D is transferred to Q. This is called latching.

- Exist with "latching" on rising and/or falling edge.

- We already talked about the NE555.

- Many variants. Parameters to look out for:

- Frequency stability

- High-Low-ratio

- Jitter: short term frequency oscillations

- Can it drive all my chips?

- Often combined with a quartz, which swings on its resonance frequency

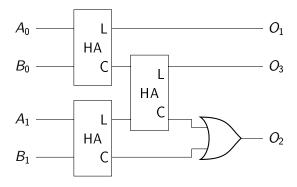

#### We want to add two 1 bit numbers to get one 2 bit output

| А | В | C(arry) | L(SB) |

|---|---|---------|-------|

| 0 | 0 | 0       | 0     |

| 0 | 1 | 0       | 1     |

| 1 | 0 | 0       | 1     |

| 1 | 1 | 1       | 0     |

#### We want to add two 1 bit numbers to get one 2 bit output

| А | В | C(arry) | L(SB) |

|---|---|---------|-------|

| 0 | 0 | 0       | 0     |

| 0 | 1 | 0       | 1     |

| 1 | 0 | 0       | 1     |

| 1 | 1 | 1       | 0     |

C = AB

L = A ⊗ B (xor)

Two two-bits to 3 bits:

Exercise: Build the truth table for this circuit!

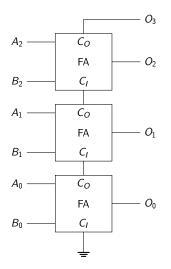

### Truth table:

| Α | В | Ci | Co | L |

|---|---|----|----|---|

| 0 | 0 | 0  | 0  | 0 |

| 0 | 0 | 1  | 0  | 1 |

| 0 | 1 | 0  | 0  | 1 |

| 0 | 1 | 1  | 1  | 0 |

| 1 | 0 | 0  | 0  | 1 |

| 1 | 0 | 1  | 1  | 0 |

| 1 | 1 | 0  | 1  | 0 |

| 1 | 1 | 1  | 1  | 1 |

### Multiple bits with the Full adder

• Slowest path is carry, which has to ripple through all FAs. Other name: Ripple carry adder RCA In addition to fixed function ICs, there exists programmable logic. The most capable version of this are called FPGA: Field Programmable Gate Arrays

- Consists of many LUTs, look-up-tables. These are the hardware realization of truth tables.

- One can program these truth tables!

- Additionally, one can program how these elements are connected to each other

- This is not the same as a CPU

We want to convert an analog signal into a binary number proportional to the size of the signal.

We want to convert an analog signal into a binary number proportional to the size of the signal. We already now a simple ADC with 1 bit output! The discriminator! We want to convert an analog signal into a binary number proportional to the size of the signal.

We already now a simple ADC with 1 bit output! The discriminator! There are many different ways to built multi-bit ADCs:

- Flash or direct conversion ADCs: Result in one clock

- Successive approximation: Result in N clocks for n bits

- $\bullet$   $\Sigma\Delta$  ADCs: 1 bit with high oversampling. Slowest, but very linear

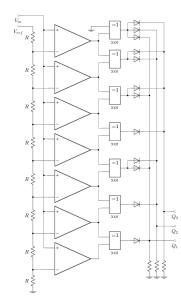

# Flash ADC

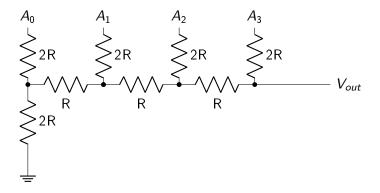

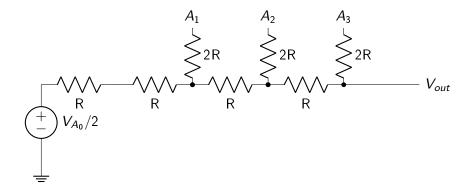

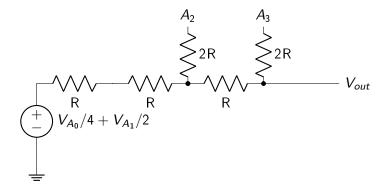

### Digital Analog Converts: DACs

$$\underbrace{ \begin{array}{c} & & \\ + \\ - \\ - \\ \end{array} }^{\mathsf{N}} V_{A_0} / 16 + V_{A_1} / 8 + V_{A_2} / 4 + V_{A_3} / 2$$